Sébastien Lafond

Simulation of Embedded Systems for Energy Consumption Estimation

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 113, January 2009

# Simulation of Embedded Systems for Energy Consumption Estimation

Sébastien Lafond

To be presented, with the permission of the Faculty of Technology of Åbo Akademi University, for public criticism in the Auditorium Gamma of the Department of Information Technologies, on February 27<sup>th</sup>, 2009, at 12 noon.

> Åbo Akademi University Department of Information Technologies Joukahainengatan 3-5 FIN-20520 Turku, Finland

> > 2009

### **Supervisor**

Professor Johan Lilius Department of Information Technologies Åbo Akademi University Joukahainengatan 3-5 FIN-20520 Turku Finland

### **Reviewers**

Professor Jarmo Takala Department of Computer Systems Tampere University of Technology Korkeakoulunkatu 1 FIN-33101 Tampere Finland

Dr. Juha-Pekka Soininen Computing and computer architectures VTT Electronics Kaitoväylä 1 FIN-90571 Oulu Finland

### Opponent

Professor Jarmo Takala Department of Computer Systems Tampere University of Technology Korkeakoulunkatu 1 FIN-33101 Tampere Finland

ISBN 978-952-12-2240-5 ISSN 1239-1883

# Abstract

Technology developments in semiconductor fabrication along with a rapid expansion of the market for portable devices, such as PDAs and mobile phones, make the energy consumption of embedded systems a major problem. Indeed the need to provide an increasing number of computational intensive applications and at the same time to maximize the battery life of portable devices can be seen as incompatible trends.

System simulation is a flexible and convenient method for analyzing and exploring the performance of a system or sub-system. At the same time, the increasing use of computational intensive applications strengthens the need to maximize the battery life of portable devices. As a consequence, the simulation of embedded systems for energy consumption estimation is becoming essential in order to study and explore the influence of system design choices on the system energy consumption.

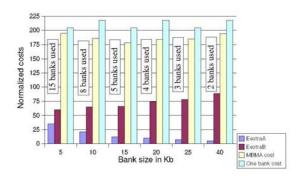

The original publications presented in the second part of this thesis propose several frameworks for evaluating the effects of particular system and software architectures on the system energy consumption. From a software point of view Java and C based applications are studied, and from a hardware perspective systems using general purpose processor and heterogeneous platforms with dedicated hardware accelerators are analyzed. Papers 1 and 2 present a framework for estimating the energy consumption of an embedded Java Virtual Machine and show how an accurate energy consumption model of Java opcodes can be obtained. Paper 3 evaluates the cost-effectiveness of Forward Error Correction algorithms in terms of energy consumption and demonstrates that a substantial energy saving is achievable in a DVB-H receiver when a FEC algorithm is used for file downloading scenarios. Paper 4 and 5 present the simulation of heterogeneous platforms and point out the drawback of different mechanisms used to synchronize a hardware accelerator used as a peripheral device. Paper 6 shows that the use of a multi-bank memory architecture can lead to a 20% static energy saving without any software optimization.

# Acknowledgements

All my gratitude goes to all who made this thesis come true. First of all, I would like to thank my supervisor, Professor Johan Lilius for his patience in addition to the invaluable support and trust he offered me during my doctoral studies. I wish to thank him for all the guidances he gave me for sailing in the world of academic research. I also wish to express my sincere gratitude to my co-authors, Jani Boutellier, Dr. Jerker Björkqvist, Kristian Nybom and Professor Olli Silvén. I am glad I had the opportunity to work with them.

I wish to thank Dr. Juha-Pekka Soininen from VTT and Professor Jarmo Takala from Tampere University of Technology for reviewing my thesis. They gave me constructive comments and useful suggestions for improving this thesis. I also wish to thank Professor Jarmo Takala to accept to act as an opponent during the public disputation of my thesis.

I am grateful to Professor Ralph-Johan Back, former Director of the Turku Centre for Computer Science (TUCS), for accepting my application to the TUCS graduate school. I am thankful for the remarkable working environment provided by the Turku Centre for Computer Science and the Department of Information Technologies at Åbo Akademi University. I gratefully acknowledge the financial support I received from the Turku Centre for Computer Science, the Center for Reliable Software Technology (CREST) and the Department of Information Technologies. I also would like to express my gratitude to the Nokia Foundation, the Emil Aaltonen Foundation and the Oscar Öflund Foundation for their generous grants.

I also greatly appreciated during my doctoral studies the enjoyable and pleasant atmosphere at the Embedded Systems Laboratory. I would like to thank the present and past members of the laboratory for all friendly and lively coffee meetings we had. I specially wish to thank Andreas, Dag, Dragos, Jerker, Johan E. and Kristian for all work-related and work-unrelated discussions we had along these years. The Embedded Systems Laboratory is not only made up of expertise (and energy), but contains also an important part of conviviality.

In addition I am grateful to my friends who made my stay in Finland a source

of happiness during the past years. I especially wish to thank the local French and *francophile* community for all the great moments we have shared. Particular thanks to Anna, Antoine, Christophe, Elina, Ellinor, Emmanuel, Eric, François, Henri, Julien, Katarzyna, Kathleen, Lionel, Marika, Nicolas, Pia, Séverine, Sirpa, Stefan, Stefanie, and Tuija for their friendship.

Finally, I also wish to express my warm thanks to my parents and my brothers Mathieu and Olivier for the constant support and encouragements I received from them over the years. Most of all, infinite thanks to my wife Beáta for her daily devotion and unlimited love.

College Park, November the 27th, 2008

Sébastien Lafond

# List of original publications

- Sébastien Lafond and Johan Lilius. An Energy Consumption Model for an Embedded Java Virtual Machine. In proceedings of the 19th International Conference on Architecture of Computing Systems - ARCS 2006, Lecture Notes in Computer Science, Vol. 3894, pages 311-325. Springer-Verlag, 2006.

- Sébastien Lafond and Johan Lilius. Energy consumption analysis for two embedded Java virtual machines. In *Journal of Systems Architecture*, volume 53, Issues 5-6, pages 328-337. Elsevier B.V., 2007.

- Sébastien Lafond, Kristian Nybom, Jerker Björkqvist and Johan Lilius. Receiver Coding Gain in DVB-H Terminals using Application Layer FEC Codes. In proceedings of the *Third International Conference on Digital Telecommunications - ICDT 2008*, pages 110-116. IEEE, 2008

- 4. Sébastien Lafond, Jani Boutellier, Johan Lilius and Olli Silvén. Energy efficiency analysis of multi-stream MPEG-4 decoder systems. In *Multimedia* on Mobile Devices 2008, proceedings of SPIE Vol. 6821, 68210G-1. SPIE, 2008

- Sébastien Lafond and Johan Lilius. Interrupt Costs in Embedded System with Short Latency Hardware Accelerators. In proceedings of the *International Conference on Engineering of Computer-Based Systems - ECBS 2008*, pages 317-325. IEEE, 2008

- Sébastien Lafond and Johan Lilius. Static Energy Saving Through Multi-Bank Memory Architecture. In proceedings of the *International Conference* on Embedded Computer Systems: Architectures, Modeling, and Simulation - ICSAMOS 2006, pages 43-49. IEEE, 2006.

# Contents

| I | Research Summary |       |                                                | 1  |

|---|------------------|-------|------------------------------------------------|----|

|   | 1                | Intro | duction                                        | 3  |

|   | 2                | Syste | m simulation for energy consumption estimation | 6  |

|   |                  | 2.1   | Instruction-level energy simulator             | 6  |

|   |                  | 2.2   | Architecture level power simulator             | 8  |

|   | 3                | Sim-  | panalyzer extensions                           | 11 |

|   |                  | 3.1   | File handling mechanism                        | 11 |

|   |                  | 3.2   | Hardware accelerators as peripheral devices    | 12 |

|   | 4                | Conc  | lusion                                         | 15 |

## **II** Original Publications

27

# Part I

# **Research Summary**

### **1** Introduction

Technology developments in semiconductor fabrication [1], along with a rapid expansion of the market for portable devices, such as PDAs and mobile phones, make the energy consumption of embedded systems a major problem [2]. Indeed the need to provide an increasing number of computational intensive applications and at the same time to maximize the battery life of portable devices can be seen as incompatible trends. Although energy is solely consumed by the hardware, energy consumption can be trimmed by adequate software manipulations because the software operates the hardware activities. Therefore, for a defined hardware platform different software implementations providing the same services can have different performance in terms of energy consumption. Evaluating these performance differences is essential for determining which implementation is the optimum solution. System simulation can be an answer to the problem of performance evaluation when assessing different software implementations on several hardware platforms, as it provides a flexible and convenient solution for performance evaluation.

#### **Energy consumption**

We can often see confusion concerning the use of the terms energy and power. The electrical energy E of a system having one source of energy is expressed in joule and is defined by:

$$E = q.V$$

where q is the quantity of electric charges expressed in coulomb that has passed through the cross-section of the electrical conductors connecting the source of energy, and V is the electric potential expressed in volt between the two poles of the source of energy. Whereas, the power P is expressed in watt and is defined as the average rate at which electrical energy is consumed by an electric circuit during a time t:

$$P = \frac{E}{t}$$

Furthermore, the overall power dissipation P can be expressed as:

$$P = P_{stat} + P_{dyn}$$

where  $P_{stat}$  represents the static power dissipation and  $P_{dyn}$  represents the dynamic power dissipation.  $P_{stat}$  is caused by the leakage current  $I_{leak}$  flowing through turned-off transistors from the supply rail to ground and is expressed for one transistor as:

$$P_{stat} = I_{leak}.V_{DS}$$

where  $V_{DS}$  is the electric potential between the drain and the source of a turnedoff transistor.  $P_{dyn}$  is due to the switching activity of the gates constituting the digital circuit. The dynamic power consumption per transistor is expressed as:

$$P_{dyn} = ar.f_c.C_l.V_{DD}^2$$

Most of the confusion comes from the use of the *low power* adjective to mean *having a low energy consumption* or *having a low average power dissipation*. For most of the system the important matter is certainly the energy consumed by the system, which is driven by its average power dissipation over its life time. Indeed, it is the energy consumed by a system that will affect its operating cost as well as its operating lifetime in the case where the system operates on a battery.

When considering a complete system, there are different levels [3, 4] where issues concerning energy consumption can be addressed:

- Low power electronics

- System architecture

- Code generation

- Software architecture

On each level, there are various ways [5, 3, 4, 6, 7, 8] of evaluating the energy consumption drained by a system and estimating the influence of a specific level. The original publications presented in the second part of this thesis focus, in papers 1, 2 and 3, on the simulation of different software architectures and, in papers 4, 5 and 6, on system architectures for embedded system.

Furthermore, as the circuits shrink, leakage currents and thus static power dissipation become increasingly significant [9]. To limit the energy due to the static power dissipated by RAM memories, paper 6 proposes, models and simulates a multi-bank memory architecture. All the other papers presented in the second part of this thesis propose several simulation platforms for estimating the dynamic energy consumed by the studied system.

#### Embedded systems and energy consumption

There are several alternatives for defining an embedded system. In [10] an embedded system definition is given based on its development environment as: *any computer system for which the primary development tools do not run on the system itself.* But in [11] an embedded system is defined based on its physical environment as: *information processing systems embedded into enclosing products such as cars, telecommunication or fabrication equipment.*

The union of these two definitions designates a complete system with dedicated software applications running on a particular hardware platform. Hence it encompasses a very large spectrum of systems ranging from small and simple systems such as a portable watch, to large and complex stationary industrial installations such as the control system of an electrostatic accelerator. The scope of this thesis targets a restricted set of embedded systems that can be defined as *stand-alone computer based systems operating on a battery for which the primary development tools can not run on the system itself.*

As the definition of an embedded system is rather large we can categorize two different types of embedded systems when we look at problems resulting from their energy consumption characteristic: a) portable devices having a strong constraint on their available energy budget, thus limiting the system average power dissipation for a defined operating time and b) stationary systems having almost no limitation concerning available energy but where the level of the heat generated by the system requires cooling solutions such as heatsink, fan or liquid cooling unit.

A portable device operates on a limited energy budget defined by the capacity of its battery. As the physical dimension of a portable device is an important design characteristic, the constraint on the physical size and weight of the battery strongly limit the available energy capacity of the battery. Therefore, for such a system the average power dissipated by the device will determine the system operating time before the battery needs to be changed or recharged. Moreover, in most of portable systems the instantaneous power dissipation is not an essential characteristic as the heat conducted and/or radiated to the device surroundings stays below acceptable limits. Also several properties of a system can be affected by a limited energy budget. Energy management through voltage and frequency scaling can affect the system reliability [12, 13], whereas the battery capacity may not cope with the energy requirement of a cryptographic algorithm [14] and as a result prevents the implementation of the required security and privacy level.

On the other hand, most of stationary systems do not rely on a battery and thus do not have strong constraints concerning their energy budget. However, for such systems the maximum instantaneous dissipated power will define the required cooling solutions in order to operate within safe temperatures.

The last two decades have seen tremendous growth in the demand for such systems with the emergence of communicators, mobile phones, PDAs, palmtops, and so on. At the same time, while the increase in performance of embedded system's hardware caused a radical increase in power densities [13], an increasing number of computational intensive applications (e.g. multimedia steaming applications) are expected to run on such systems [15]. While introducing more complex applications and application execution platforms, these parallel trends make energy-aware system design, and thus system simulation for energy consumption estimation, a fundamental issue.

### **2** System simulation for energy consumption estimation

System simulation is a widely used method for gathering information about system performances without the need to have the system physically available. The need of system simulation arose concurrently with the fast development of computer systems in the seventieth [16, 17]. Compared to the use of a prototype board, system simulation provides a flexible and convenient solution for performance evaluation during the system design process. Historically system simulation was principally developed and used for simulating the execution time and the memory requirement of a system [18, 19, 20, 21]. However, technology developments in semiconductor fabrication [1] along with a rapid expansion of the market for portable devices make the energy consumption a major problem for embedded systems to operate on a battery [2]. Most of the simulation frameworks for energy consumption estimation can be categorized either as, an instruction-level energy simulator or, an architecture level power simulator.

#### 2.1 Instruction-level energy simulator

The possibility of simulating the energy consumption of a processor based on an instruction-level power model is first introduced in [5] by Tiwari at al. In [5], they develop a power analysis technique for two microprocessors, the Intel 486DX2 and Fujitsu SPARClite 934, and measure the average current drained by the processor for each instruction from the processor instruction set. These measured values give the base energy cost for each instruction. In addition to the base energy cost, inter-instruction effects are also analyzed. Inter-instruction effects are due to cache misses, resource constraints and circuit state. A cache miss introduces extra latency when the data is fetched from memory because the data needs to be retrieved from a lower level memory. In the same way, a resource constraint can cause pipeline and buffer stalls which lead to an increase in the number of cycles needed to execute a sequence of instructions. These two inter-instruction effects increase the system energy consumption by introducing extra time in the software execution. On the other hand, based on the previous state and the instruction operand values, the effect of the circuit state will modify the base energy cost for each instruction execution without introducing any extra cycle penalty.

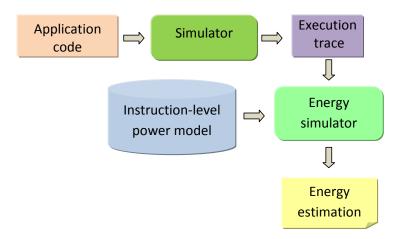

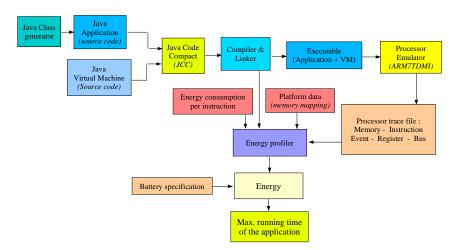

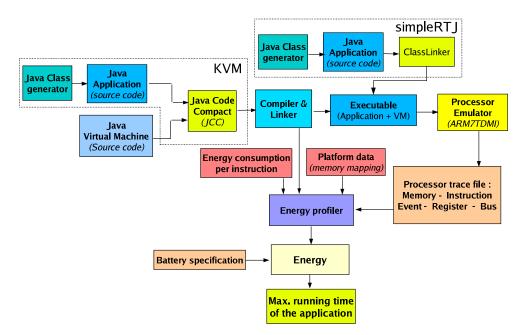

Several instruction-level energy simulators have been presented since [5] in [6, 22, 23, 24, 25, 26]. These simulators are all based on the same approach presented in [5] and illustrated in figure 1: an instruction-level power model is obtained by physical measurements of the current drained by the processor, and external memory if a memory model is also given, and the energy consumption of an application is estimated based on a simulated execution trace containing the list of executed instructions.

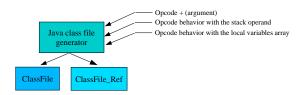

To the author's knowledge the possibility of establishing an opcode-level energy model for a Java Virtual Machine was not previously studied. Following a similar

Figure 1: General approach used by instruction-level energy simulators

approach to that used in [5] to determine an instruction-level energy simulator for a processor, paper 1 and 2 describe the development of a framework used to establish an opcode-level energy model for embedded Java Virtual Machines.

Paper 1 proposes a general framework for estimating the energy consumption of an embedded Java Virtual Machine (JVM). This paper presents a number of experiments to estimate the constant overhead of the JVM energy consumption and establishes an energy consumption cost for individual Java Opcodes. The first author is responsible alone for all the results and contributions of this publication.

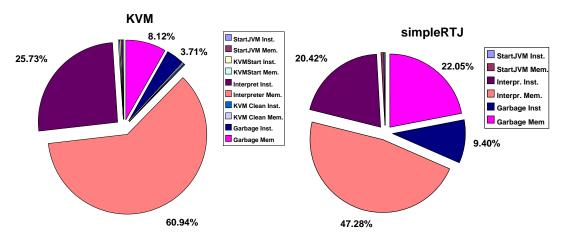

Paper 2 extents the results presented in paper 1. In paper 2, a comparison between the Sun Microsystems K Virtual Machine (KVM) and the simple Real-Time-Java (simpleRTJ) virtual machine is done. This publication shows that implementation differences between two embedded Java Virtual Machines can lead to great divergence regarding the JVM energy consumption. The first author is responsible alone for all the results and contributions of this publication.

Due to space requirement the result tables of papers 1 and 2 were initially only published on the internet, but they are, in this thesis, included as an appendix at the end of each paper.

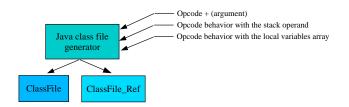

Instead of using the physical measurements of the current drained by the applications we used the commercial ARMulator [27] as the processor simulator and the enprofiler tool [28, 29] as the energy simulator. This choice was motivated by the advantage given by the use of a simulated environment and also the fact that the enprofiler tool provides satisfactory precision [29] when estimating the energy consumed by the execution of an application. As for establishing the base energy cost for processor instructions in [5], the cost of each Java opcode is determined by looking at the cost differences between the execution of two particular Java classes. As the generation by hand of a Java class is an extremely tedious task, a Java class file generator producing particular pairs of Java classes was developed to extract

the energy consumption of a singular Java opcode.

Nevertheless, the inter-instruction effect due to the circuit state between two Java opcodes is negligible compared to the one at the processor instruction level. This can be explained by the corresponding code length in processor instructions of one Java opcode, ranging from 45 to few thousands processor instructions. As the inter-instruction effect, due to the circuit state, appears only between the last and first processor instructions of two consecutive Java opcodes, its value becomes insignificant in comparison to the cost of execution of the block of processor instructions corresponding to one Java opcode.

The opcode-level energy models presented in paper 1 and 2 are validated based on the execution of benchmarks [30]. For each benchmark execution the total energy costs given by the established models are compared to the energy cost given by the enprofiler energy simulator. Based on these observations the opcode-level energy models give results with an error range of -5% +10% compared to the enprofiler result. This loss in precision has to be balanced with the considerable gain in execution speed between both simulations. It takes only few seconds to compute the total energy cost of an application based on the proposed opcode-level energy models, compared to several hours needed by the enprofiler simulator.

#### 2.2 Architecture level power simulator

A different approach to the simulation of processor energy consumption is to develop an architecture based energy model [31, 32, 33, 34, 35, 36]. With this approach each functional unit, also called a micro-architectural block, present in the processor is modeled, and the total energy consumption is estimated at every clock cycle by summing up the energy consumed by each functional unit.

#### **Conventional Architecture**

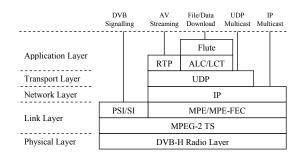

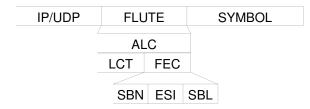

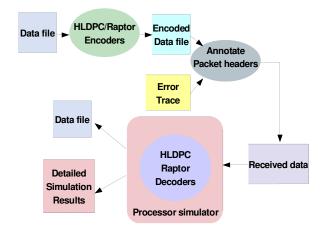

In paper 3 the simulation of a conventional architecture, containing a general purpose processor and a standard memory architecture composed by a main memory and two cache levels, is needed in order to simulate forward error correction (FEC) algorithms.

Because Sim-panalyzer [37] is a widely used [38, 39, 40, 41] and open-source cycle-accurate architecture level energy simulator, Sim-panalyzer was chosen for simulating the FEC algorithm. Sim-panalyzer was developed on top of the simoutorder simulator, a component within the SimpleScalar-ARM simulator [42], and simulates a strongARM SA1100 processor. It computes the energy dissipation of each micro-architectural block by multiplying the switching capacitance by the number of micro-architectural accesses [43]. Sim-panalyzer simulates a configurable level one and two, data and instruction, cache memories. For each cache the associativity, the number of blocks and the block size can be configured. Moreover, the data and instruction caches from the same level can be unified. Sim-panalyzer provides accurate results with a 9% error margin in its datapath and execution unit models and a 7% error margin in its memory power model compared to a gate level simulation [43].

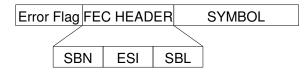

FEC [44] is a technique used in telecommunication for detecting and recovering errors in the transmitted information without the need to request the sender for additional data. On the sender side, FEC algorithms add redundant data to the transmitted information in a way that retransmission of the information can often be avoided. FEC algorithms have been widely studied across all telecommunication domains [45, 46, 47, 48]. All these studies analyze the performance of FEC algorithms by analyzing the algorithm complexity, the size of the redundant data and the remaining loss probability depending on the erasure rate in the transmission channel. However, to the author's knowledge, no analysis was done in order to evaluate the cost-effectiveness of FEC algorithm in terms of energy consumption in the receiver.

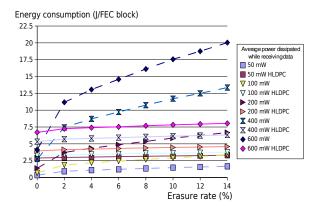

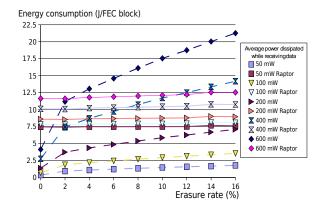

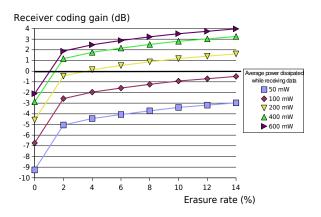

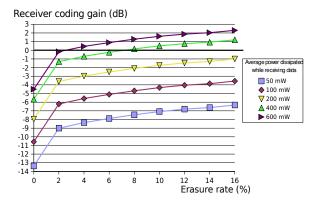

Paper 3 defines the receiver coding gain, the reduction of energy while using coding compared to the energy needed without coding, for a DVB-H receiver in file downloading scenarios. Moreover, an evaluation of the cost-effectiveness of FEC algorithms in terms of energy consumption in the receiver is presented.

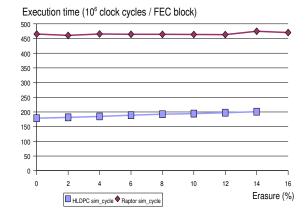

This publication presents a comparative study between two AL-FEC codes, the HLDPC and the Raptor code, as well as a theoretical analysis of the receiver coding gain. This paper shows that depending on the AL-FEC code and the erasure rate the receiver coding gain varies from -9 to 4 dB. It demonstrates that for one of the studied AL-FEC code, and the present technology for DVB demodulator, the use of application layer coding leads to a positive receiver coding gain when the erasure rate is above 2%. The first author contributed to a significant part of the results and contributions of this publication.

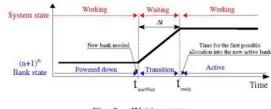

#### Simulation of heterogeneous platforms

Different solutions have been proposed for simulating heterogeneous platforms. In [49] Ptolemy, a well-known environment for simulation and prototyping of heterogeneous systems, is presented. Ptolemy focuses on particular type of system domains including synchronous and dynamic dataflow, and discrete-event systems.

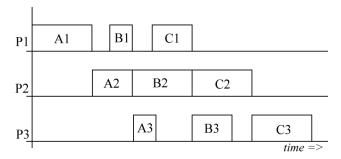

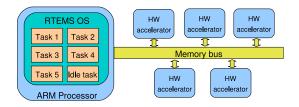

In paper 4 and 5 the simulation of an application written in C and running on a heterogeneous platform is required. The objective of paper 4 and 5 focus only on the impact of the hardware platform on the system energy consumption. The software implementation of the applications existed "as it is", but the use of Ptolemy would require a Ptolemy specific re-implementation of them. Therefore, an extension of the general purpose processor simulator Sim-panalyzer was implemented instead of re-implementing the existent applications for Ptolemy.

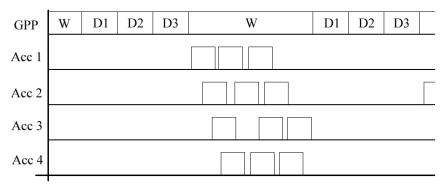

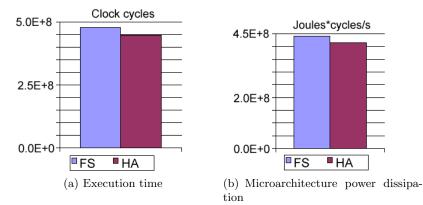

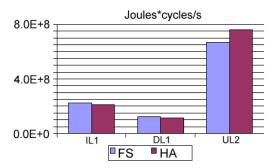

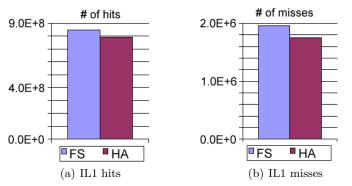

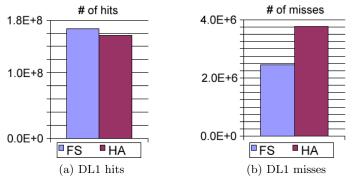

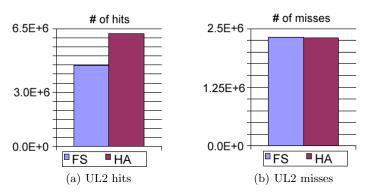

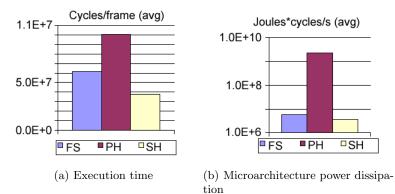

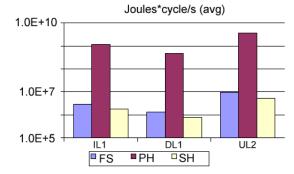

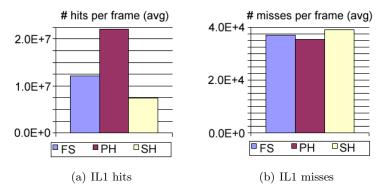

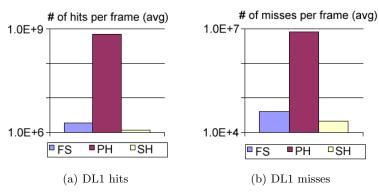

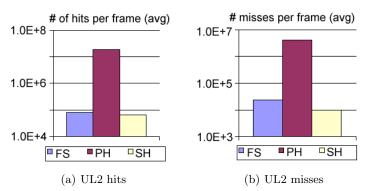

Paper 4 presents an analysis of three systems simultaneously decoding multi-

ple videos on a dedicated heterogeneous platform. The compared systems consist of one fully software and two hardware accelerated solutions. One of the hardware accelerated solutions is using flag polling for synchronizing the processing units, while the other one is using a scheduling-based synchronization approach. This publication analyzes the differences between the three video decoding systems in terms of execution speed, energy consumption and cache behaviors. The first author contributed to a significant part of the results and contributions of this publication.

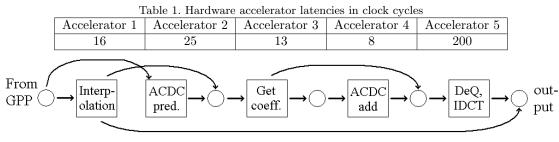

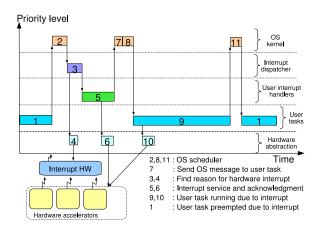

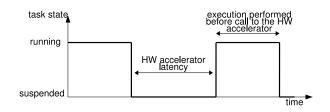

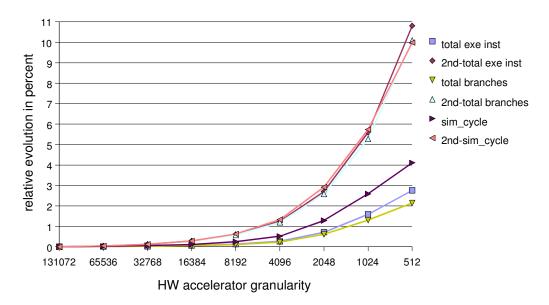

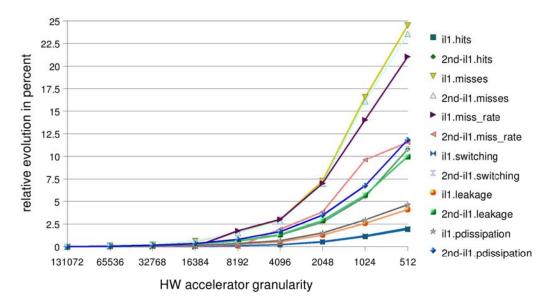

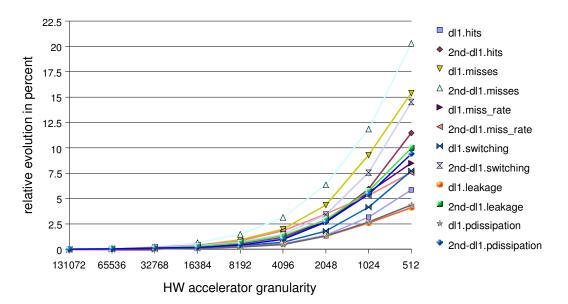

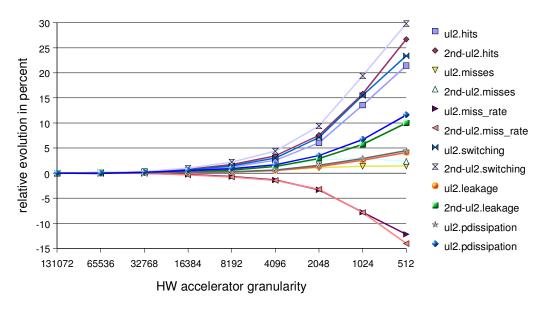

In paper 5 a methodology for analyzing the impact of short latency hardware accelerators on a typical embedded system is proposed. This publication analyzes the effect of the hardware accelerator granularity on the system performance with respect to the number of cache misses, the execution time and the system energy consumption. This paper demonstrates the relative important costs introduced by the mechanism for suspending a task in a real-time operating system when the hardware accelerator granularity is decreasing. The first author is responsible alone for all the results and contributions of this publication.

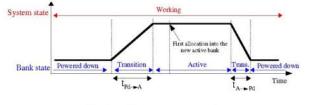

#### Memory architecture

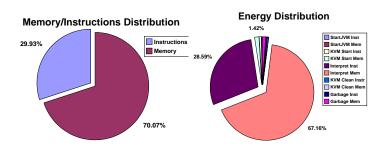

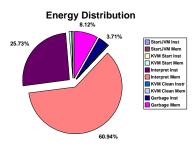

The simulation of memories includes the simulation of CPU caches and main memories, and is relevant for most of the systems if one wants to obtain comprehensive data about the system performances. For instance papers 1 and 2 show that memory accesses consume 70% of the total energy consumption of the studied system. This reflects the importance of memory performances for stack-based machines where all operand variables and operation results are stored on the stack. Also paper 5 demonstrates the potential negative effect of caches when short latency hardware accelerators are used. This is due to an increase in the number of cache misses imputable to the relative short interval between two context switches.

Many studies concerning CPU cache configurations and simulations [50, 51, 52, 53] were done since the 1980s when the performance gap between processors and memories started to be significant [54]. Also the exploration and the simulation of different memory architectures have been extensively studied [55, 56, 57, 20, 58, 59]. As well, studies concerning multi-bank memory architectures have been presented [60, 61]. However, none of these studies propose a model for the static energy consumed by a multi-bank memory architecture.

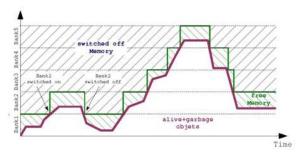

Paper 6 establishes the static energy model for a multi-bank memory architecture and introduces the equations governing the optimization problem for decreasing its static energy consumption. The impact of different parameters on the energy consumption and a performance analysis of such memory architecture in terms of static energy consumption and execution speed is also presented. This paper shows that the use of a multi-bank memory architecture can lead to a 20% static energy saving without any software optimization, nor bank need prediction, nor dedicated allocation policy. It also highlights the predominant role of the bank occupation

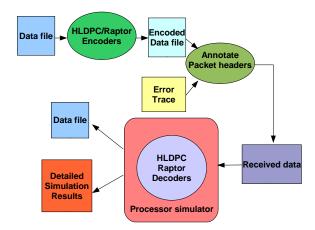

Figure 2: General view illustrating the measurement system used in paper 3

rate in the multi-bank memory architecture static energy consumption. The first author is responsible alone for all the results and contributions of this publication.

### **3** Sim-panalyzer extensions

Sim-panalyzer is the processor simulator used in papers 3, 4 and 5. However, in order to simulate the desired hardware platforms and/or software components several extensions were implemented into sim-panalyzer. As these extensions are not discussed in papers 3, 4 and 5 due to space requirement, the following section presents them in more detail.

#### 3.1 File handling mechanism

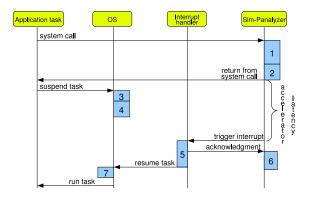

In paper 3, a possible receiver coding gain in terms of energy consumption is studied when error correction at the application layer (AL-FEC) is used in file downloading scenarios over DVB-H. In order to be able to compare the energy consumption of a receiver using AL-FEC with a receiver having no error correction at the application layer, the execution cost of the AL-FEC codes needs to be evaluated. In a physical system the encoded data is received in a streaming manner from the radio receiver via a buffer. However, because AL-FEC codes for DVB-H receiver are for the moment only at a development stage and not used in real devices, the simulated algorithms were implemented with file handling mechanism for fetching the received data. Figure 2 presents the measurement system used in paper 3 where data files are represented by a rectangle box.

The received data file size being relatively important, fetching the encoded data from a file would distort the results given by the simulator. Therefore, in order to

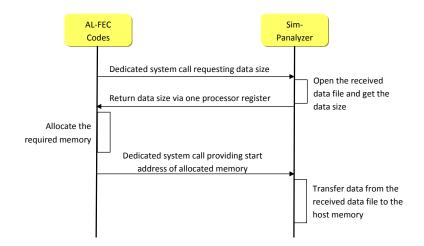

minimize the disturbance from the file handling mechanism in the simulation of the AL-FEC codes, the Sim-panalyzer and AL-FEC codes were modified. The process of fetching the received data from a file has been moved to the simulator and only the size of the received data and a memory address are exchanged between the simulator and the AL-FEC codes via dedicated system call. Figure 3 shows the sequence diagram describing the new required operations for execution the file handling process within the simulator. Basically, in the AL-FEC codes the following code needs to be used instead of the open file command:

In this code the dedicated system calls are implemented with software interrupt and parameter values are passed via registers. The software interrupt number 0x200 is used to implement the system call requesting the data size and the software interrupt number 0x201 is used to implement the system call providing the start address of the memory space allocated for the received data. On the Simpanalyzer side, a switch statement implements the required functionalities for the software interrupt numbers 0x200 and 0x201. With such implementation the disturbance from the file handling mechanism in the simulation of the AL-FEC codes is minimized.

#### 3.2 Hardware accelerators as peripheral devices

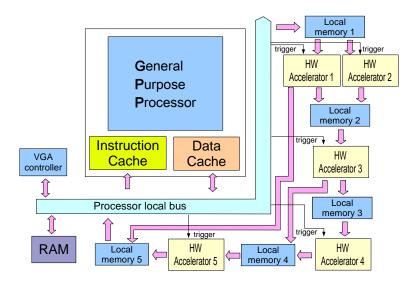

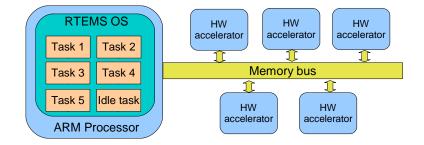

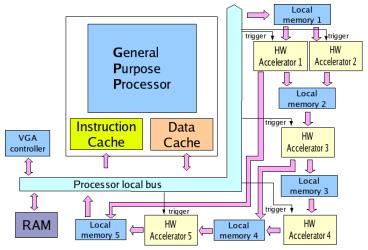

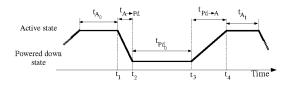

In papers 4 and 5 the simulated hardware platforms consist of a general purpose processor and a set of dedicated hardware accelerators used as peripheral devices. Figures 4 and 5 present the simulated platforms in respectively paper 4 and 5. In order to simulate the use of a hardware accelerator, a new system call and new interrupt service routine, in the case the accelerator must be synchronized by interrupt, has to be implemented.

Each hardware accelerator is triggered via a system call (implemented with a software interrupt) and if needed, signals the completion of its job by setting up the corresponding hardware interrupt.

Data transfer from the general purpose processor to an accelerator can be done via the processor registers if only few atomic variable values are passed. A predefined shared memory space is used for transferring several atomic variables or full

Figure 3: Sequence diagram - Dedicated communication between AL-FEC codes and Sim-Panalyzer

data structures from the general purpose processor to an accelerator. For transferring the accelerator result(s) to the general purpose processor a second predefined shared memory space is used.

Sim-panalyzer was modified in order to support the use of these predefined shared memory spaces. The implementation of dedicated system calls used to trigger the hardware accelerator executions is the same as the one presented in the previous *File handling mechanism* subsection. The use of new interrupt service routines requires few modifications in the Sim-panalyzer simulator and the RTEMS operating system. Sim-panalyzer was modified in order to assign, for each accelerator generating an interrupt, a distinctive interrupt mask to the current program status register (CPSR) when the processor is to be put in interrupt mode. In RTEMS, the interrupt handler was modified to identify, based on the interrupt mask, the interrupt source and to call the appropriate interrupt service routine (ISR).

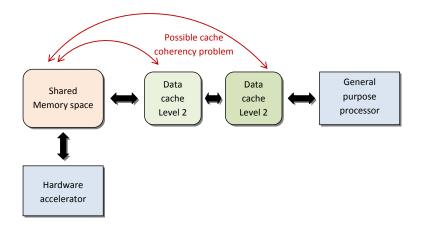

Because the general purpose processor and the hardware accelerators are sharing the same memory space for data transfer, a cache coherency problem may arise. Figure 6 illustrates the possible problem of cache coherency between the data stored in level one and two caches and the corresponding data stored in the shared memory space. Without any mechanism for avoiding cache coherency problem, the integrity of a data is not insured for a data moved by the GPP to the shared memory space. Indeed, Sim-Panalyzer implements only the write-back mechanism for cache operations. Thus, a data value is updated in a shared memory space only when the corresponding memory location is not present or evicted from the cache level one or two. The same is true for a data moved by the accelerator to the shared memory. If the corresponding memory location is present in cache level one or two when the GPP accesses the data, the outdated data value from the cache will

Figure 4: The heterogeneous platform simulated in paper 4

be used instead of the value computed by the accelerator.

In order to avoid cache coherency issues, Sim-Panalyzer was modified to support uncacheable memory locations. Accesses to these uncacheable memory locations are simulated as they would directly access the shared memory location without going through the caches. In order to reserve these shared memories in the simulated memory space, and also to make the simulation of different architectures possible without the need of re-compiling the simulator, the shared memory spaces are statically allocated within the RTEMS initialization phase. The start addresses of the created shared memories are then passed to the simulator via a dedicated system call.

Figure 5: The heterogeneous platform simulated in paper 5

Figure 6: Cache coherency problem on a typical heterogeneous platform

### 4 Conclusion

The increasing number of computational intensive applications strengthens the need to maximize the battery life of portable devices. As a consequence, the simulation of embedded systems for energy consumption estimation is becoming essential if one wants to study and explore the influence of system design choices on the system energy consumption. The original publications presented in the second part of this thesis propose several frameworks for evaluating the effects of particular system and software architectures on the system energy consumption. From a software point of view Java and C based applications are studied, and from a hardware perspective systems using a general purpose processor or a heterogeneous platform with dedicated hardware accelerators are analyzed.

Papers 1 and 2 present a general framework for estimating the energy consumption of an embedded Java Virtual Machine (JVM), and establish an energy consumption cost for individual Java Opcodes. The presented opcode-level energy models are validated and provide results with an error range of -5% +10% compared to an established processor instruction-level energy simulator. However, this loss in precision is balanced by the considerable gain in execution speed between both simulations. Papers 1 and 2 can also guide developers to produce an energyaware java application by for example limiting the use of long data type, avoiding multidimensional array and trying to use consecutive case values inside a switch statement. Moreover, the results of paper 1 and 2 can be further used for developing estimation frameworks for profiling and predicting Java application energy consumption. To the author's knowledge the results presented in papers 1 and 2 are used in the development of an energy estimation framework in [62, 63, 64].

Paper 3 defines the receiver coding gain for a DVB-H terminal in file downloading scenarios, and evaluates the cost-effectiveness of FEC algorithms in terms of energy consumption. This publication demonstrates that a substantial energy saving is achievable in a DVB-H receiver when a forward error correction algorithm is used for file downloading scenarios. Providing an erasure model for a DVB-H network, the presented results can be used for estimating the feasible energy gain, or loss, depending on the position of the DVB-H receiver within the network.

The simulation of heterogeneous platforms is presented in paper 4 and 5. Three systems simultaneously decoding multiple videos on a dedicated heterogeneous platform are simulated in Paper 4, while paper 5 proposes a methodology for analyzing the impact of short latency hardware accelerators on a typical embedded system. Both papers point out the drawback of different mechanisms used to synchronize a hardware accelerator used as a peripheral device. Paper 4 indicates poor performance when synchronization is performed by pooling the state of a frequently accessed accelerator, and paper 5 indicates poor performance when synchronization of a short latency accelerator is achieved with interrupt. These results can help choosing the adequate synchronization mechanism for a hardware accelerator used as a peripheral device depending on its latency and usage frequency.

Because paper 3, 4 and 5 use the cycle-accurate architecture level energy simulator Sim-Panalyzer, the presented energy consumption results carry the error margin created by Sim-Panalyzer. However, with a 9% error margin in its datapath and execution unit models and a 7% error margin in its memory power model [43], Sim-panalyzer can be considered as an accurate simulator.

The static energy model for a multi-bank memory architecture and the equations governing the optimization problem for decreasing the static energy consumed by the memory architecture are presented in paper 6. This paper shows that the use of a multi-bank memory architecture can lead to a 20% static energy saving without any software optimization, nor bank need prediction, nor dedicated allocation policy. This static energy model provides the needed model if one wants to estimate the static energy consumed by a multi-bank memory architecture for a specific bank size and allocation trace.

All papers in the second part of this thesis present simulation based energy estimation approaches. The common benefit of system simulation is the ability to gather information about system performance without the need to have the system physically available. Without a simulation based approach some of the studies presented in the papers would have been complicated to conduct. This is especially true for estimating the heterogeneous platforms presented in paper 4 and 5, as well as the multi-bank memory architecture presented in paper 6. Indeed, manufacturing such platforms or memory architecture is an extremely time consuming process. During the process of system design, it is evident that the simulation of such systems is faster and more viable than manufacturing system prototypes. However, even if using a simulation based approach can be a considerably faster and cheaper approach than physically manufacturing the system, it can not always be considered as the ideal solution. First of all, there is always the need of assessing the accuracy of an estimation based approach, which means that the results from the simulation tool need to be compared to a reference. But, in most of the cases the only reliable reference that can be used is the physical system itself. In papers 1 and 2 we also show that depending on which level the simulation approach is based, the time needed to actually run the simulation process can vary considerably. Simulating a small Java application at the processor instruction level takes several hours, whereas it takes only few second at Java opcode level. This shows that the choice of using system simulation over physical measurement must be based on the obtainable simulation speed, the number of needed simulations and the complexity of manufacturing or obtaining the studied system. However, with a growing demand for reusable hardware and software feature, mainly due to a reduction in the design to market time, we can predict that demands for system simulations performed on a high level of abstraction will most probably grow.

# Bibliography

- Jayanth Srinivasan, Sarita V. Adve, Pradip Bose, and Jude A. Rivers. The impact of technology scaling on lifetime reliability. In DSN '04: Proceedings of the 2004 International Conference on Dependable Systems and Networks, page 177, Washington, DC, USA, 2004. IEEE Computer Society.

- [2] David M. Brooks, Pradip Bose, Stanley E. Schuster, Hans Jacobson, Prabhakar N. Kudva, Alper Buyuktosunoglu, John-David Wellman, Victor Zyuban, Manish Gupta, and Peter W. Cook. Power-aware microarchitecture: Design and modeling challenges for next-generation microprocessors. *IEEE Micro*, 20(6):26–44, 2000.

- [3] Gang Qu, Naoyuki Kawabe, Kimiyoshi Usami, and Miodrag Potkonjak. Function-level power estimation methodology for microprocessors. In DAC '00: Proceedings of the 37th conference on Design automation, pages 810– 813, New York, NY, USA, 2000. ACM.

- [4] Marcello Lajolo, Anand Raghunathan, Sujit Dey, Luciano Lavagno, and Alberto Sangiovanni-vincentelli. Efficient power estimation techniques for hw/sw systems. In *IEEE Alessandro Volta Memorial Workshop on Low-Power Design*, pages 191–199, 1999.

- [5] Vivek Tiwari, Sharad Malik, and Andrew Wolfe. Power analysis of embedded software: a first step towards software power minimization. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 2(4):437–445, 1994.

- [6] Tajana Šimunić, Luca Benini, and Giovanni De Micheli. Cycle-accurate simulation of energy consumption in embedded systems. In DAC '99: Proceedings of the 36th Design Automation Conference, pages 867–872, New York, NY, USA, 1999. ACM.

- [7] Anantha P. Chandrakasan, Samuel Sheng, and Robert W. Brodersen. Low power cmos digital design. *IEEE Journal of Solid State Circuits*, 27:473– 484, 1992.

- [8] Ralf Kakerow. Low power design methodologies for mobile communication. In *ICCD '02: Proceedings of the 2002 IEEE International Conference on*

*Computer Design: VLSI in Computers and Processors (ICCD'02)*, pages 8–13, Washington, DC, USA, 2002. IEEE Computer Society.

- [9] J. Adam Butts and Gurindar S. Sohi. A static power model for architects. In MICRO 33: Proceedings of the 33rd annual ACM/IEEE international symposium on Microarchitecture, pages 191–201, New York, NY, USA, 2000. ACM.

- [10] Pieter A. Olivier. Embedded system simulation: testdriving the toolbus. Technical report, Universiteit van Amsterdam (Netherlands), 1996.

- [11] Peter Marwedel. Embedded System Design. Springer-Verlag New York, Inc., Secaucus, NJ, USA, 2006.

- [12] Dakai Zhu, R. Melhem, and D. Mosse. The effects of energy management on reliability in real-time embedded systems. In *ICCAD '04: Proceedings of the* 2004 IEEE/ACM International conference on Computer-aided design, pages 35–40, Washington, DC, USA, 2004. IEEE Computer Society.

- [13] Dakai Zhu and Hakan Aydin. Energy management for real-time embedded systems with reliability requirements. In *ICCAD '06: Proceedings of the* 2006 IEEE/ACM international conference on Computer-aided design, pages 528–534, New York, NY, USA, 2006. ACM.

- [14] Nachiketh R. Potlapally, Srivaths Ravi, Anand Raghunathan, and Niraj K. Jha. Analyzing the energy consumption of security protocols. In *ISLPED '03: Proceedings of the 2003 international symposium on Low power electronics and design*, pages 30–35, New York, NY, USA, 2003. ACM.

- [15] Daler Rakhmatov and Sarma Vrudhula. Energy management for batterypowered embedded systems. *Trans. on Embedded Computing Sys.*, 2(3):277– 324, 2003.

- [16] Gary J. Nutt. The simulation of computer systems in a university environment. In ANSS '74: Proceedings of the 2nd symposium on Simulation of computer systems, pages 25–29, Piscataway, NJ, USA, 1974. IEEE Press.

- [17] M. H. MacDougall. Computer system simulation: An introduction. ACM Computing Surveys (CSUR), 2(3):191–209, 1970.

- [18] Mendel Rosenblum, Stephen A. Herrod, Emmett Witchel, and Anoop Gupta. Complete computer system simulation: The simos approach. *IEEE Parallel and Distributed Technology: Systems and Applications*, 3:34–43, 1995.

- [19] Carl J. Mauer, Mark D. Hill, and David A. Wood. Full-system timing-first simulation. In SIGMETRICS '02: Proceedings of the 2002 ACM SIGMET-RICS international conference on Measurement and modeling of computer systems, pages 108–116, New York, NY, USA, 2002. ACM.

- [20] Jie Tao, Martin Schulz, and Wolfgang Karl. A simulation tool for evaluating shared memory systems. In ANSS '03: Proceedings of the 36th annual symposium on Simulation, page 335, Washington, DC, USA, 2003. IEEE Computer Society.

- [21] P. Magnusson and B. Werner. Efficient memory simulation in simics. In ANSS '95: Proceedings of the 28th Annual Simulation Symposium, page 62, Washington, DC, USA, 1995. IEEE Computer Society.

- [22] Mariagiovanna Sami, Donatella Sciuto, Cristina Silvano, and Vittorio Zaccaria. Instruction-level power estimation for embedded vliw cores. In *CODES* '00: Proceedings of the eighth international workshop on Hardware/software codesign, pages 34–38, New York, NY, USA, 2000. ACM.

- [23] Yanbing Li and Jörg Henkel. A framework for estimation and minimizing energy dissipation of embedded hw/sw systems. In DAC '98: Proceedings of the 35th annual conference on Design automation, pages 188–193, New York, NY, USA, 1998. ACM.

- [24] Marlene Wan, Yuji Ichikawa, David Lidsky, and Jan Rabaey. An energy conscious methodology for early design exploration of heterogeneous dsps. In *CICC'98: Proceedings of the IEEE Custom Integrated Circuits Conference*, pages 111–117, May 1998.

- [25] C. Brandolese, W. Fomacian, F. Salice, and D. Sciuto. An instruction-level functionality-based energy estimation model for 32-bits microprocessors. In DAC '00: Proceedings of the 37th Design Automation Conference, pages 346–350, 2000.

- [26] Jeffry T. Russell and Margarida F. Jacome. Software power estimation and optimization for high performance, 32-bit embedded processors. In *ICCD* '98: Proceedings of the International Conference on Computer Design, pages 328–333, Oct 1998.

- [27] ARM Ltd. ARM Instruction Set Simulator ARMUlator. http://www.arm.com/support/ARMulator.html.

- [28] Enprofiler home page: http://ls12-www.cs.tu-dortmund.de/research/activities/encc/.

- [29] Stefan Steinke, Markus Knauer, Lars Wehmeyer, and Peter Marwedel. An accurate and fine grain instruction-level energy model supporting software optimization. In *Proceedings of the Internationl Workshop: Power and Timing Modeling, Optimization and Simulation (Patmos)*, 2001.

- [30] J. A. Mathew, P. D. Coddington, and K. A. Hawick. Analysis and development of java grande benchmarks. In JAVA '99: Proceedings of the ACM 1999 conference on Java Grande, pages 72–80, New York, NY, USA, 1999. ACM.

- [31] David Brooks, Vivek Tiwari, and Margaret Martonosi. Wattch: A framework for architectural-level power analysis and optimizations. In *Proceedings of the 27th International Symposium on Computer Architecture*, pages 83–94, 2000.

- [32] W. Ye, N. Vijaykrishnan, M. Kandemir, and M. J. Irwin. The design and use of simplepower: a cycle-accurate energy estimation tool. In *DAC '00: Proceedings of the 37th conference on Design automation*, pages 340–345, New York, NY, USA, 2000. ACM.

- [33] Rita Yu Chen, Robert M. Owens, Mary Jane Irwin, R. S. Bajwa, and Raminder S. Bajwa. Validation of an architectural level power analysis technique. In DAC '98: Proceedings of the 35th annual conference on Design automation, pages 242–245, New York, NY, USA, 1998. ACM.

- [34] Rita Yu Chen, Mary Jane Irwin, and Raminder S. Bajwa. Architecture-level power estimation and design experiments. *ACM Transactions on Design Automation of Electronic Systems (TODAES)*, 6(1):50–66, 2001.

- [35] Ping-Wen Ong and Ran-Hong Yan. Power-conscious software design-a framework for modeling software on hardware. In *Proceedings of the 1994 IEEE Symposium on Low Power Electronics*, pages 36–37, Oct 1994.

- [36] Toshinori Sato, Masato Nagamatsu, and Haruyuki Tago. Power and performance simulator: Esp and its application for 100 mips/w class risc design. In *Proceedings of the IEEE Symposium on Low Power Electronics*, pages 46–47, Oct 1994.

- [37] The simplescalar-arm power modeling project home page: http://www.eecs.umich.edu/~panalyzer.

- [38] Chunling Hu, Daniel A. Jimenez, and Ulrich Kremer. Toward an evaluation infrastructure for power and energy optimizations. In *IPDPS '05: Proceedings of the 19th IEEE International Parallel and Distributed Processing Symposium*, page 230.2, Washington, DC, USA, 2005. IEEE Computer Society.

- [39] Allen C. Cheng and Gary S. Tyson. An energy efficient instruction set synthesis framework for low power embedded system designs. *IEEE Transactions* on Computers, 54(6):698–713, 2005.

- [40] Johann Großädl, Stefan Tillich, Christian Rechberger, Michael Hofmann, and Marcel Medwed. Energy evaluation of software implementations of block ciphers under memory constraints. In DATE '07: Proceedings of the conference

*on Design, automation and test in Europe*, pages 1110–1115, San Jose, CA, USA, 2007. EDA Consortium.

- [41] Radu Cornea, Alex Nicolau, and Nikil Dutt. Video stream annotations for energy trade-offs in multimedia applications. In *ISPDC '06: Proceedings of the Proceedings of The Fifth International Symposium on Parallel and Distributed Computing*, pages 17–23, Washington, DC, USA, 2006. IEEE Computer Society.

- [42] Todd Austin, Eric Larson, and Dan Erns. Simplescalar: an infrastructure for computer system modeling. *Computer*, 35(2):59–67, Feb 2002.

- [43] Sim-panalyzer 2.0 reference manual. Technical report, University of Michigan, University of Colorado.

- [44] Vijay K. Bhargava. Forward error correction schemes for digital communications. *Communications Magazine*, *IEEE*, 21(1):11–19, Jan 1983.

- [45] Joachim Hagenauer and Erich Lutz. Forward error correction coding for fading compensation in mobile satellite channels. *IEEE Journal on Selected Areas in Communications*, 5(2):215–225, Feb 1987.

- [46] Rohit Puri, K. Ramchandran, K. W. Lee, and V. Bharghavan. Forward error correction (fec) codes based multiple description coding for internet video streaming and multicast. *Signal Processing: Image Communication*, 16(8):745 – 762, 2001.

- [47] Bernd Lamparter, Otto Bohrer, Wolfgang Effelsberg, and Volker Turau. Adaptable forward error correction for multimedia data streams. Technical report, Reihe Informatik 9/93, Universitat Mannheim, 1993.

- [48] Jean-Chrysostome Bolot, Sacha Fosse-Parisis, and Don Towsley. Adaptive fec-based error control for internet telephony. In *INFOCOM '99: Proceedings of the eighteenth Annual Joint Conference of the IEEE Computer and Communications Societies.*, pages 1453–1460, 1999.

- [49] Joseph Buck, Soonhoi Ha, Edward A. Lee, and David G. Messerschmitt. Ptolemy: a framework for simulating and prototyping heterogeneous systems. In *Readings in hardware/software co-design*, pages 527–543. Kluwer Academic Publishers, Norwell, MA, USA, 2002.

- [50] Rabin A. Sugumar and Santosh G. Abraham. Set-associative cache simulation using generalized binomial trees. ACM Transactions on Computer Systems (TOCS), 13(1):32–56, 1995.

- [51] Jie Tao and Wolfgang Karl. Detailed cache simulation for detecting bottleneck, miss reason and optimization potentialities. In *Valuetools '06: Proceedings of the 1st international conference on Performance evaluation methodolgies and tools*, page 62, New York, NY, USA, 2006. ACM.

- [52] Erik Berg and Erik Hagersten. Sip: Performance tuning through source code interdependence. In Euro-Par '02: Proceedings of the 8th International Euro-Par Conference on Parallel Processing, pages 177–186, Paderborn, Germany, August 2002.

- [53] Margaret Martonosi, Anoop Gupta, and Thomas E. Anderson. Tuning memory performance of sequential and parallel programs. *IEEE Computer*, 28(4):32–40, 1995.

- [54] Nihar R. Mahapatra and Balakrishna Venkatrao. The processor-memory bottleneck: problems and solutions. ACM Crossroads, 5:2, 1999.

- [55] Wei Wang, Qigang Wang, Wei Wei, and Dong Liu. Modeling and evaluating heterogeneous memory architectures by trace-driven simulation. In MAW '08: Proceedings of the 2008 workshop on Memory access on future processors, pages 369–376, New York, NY, USA, 2008. ACM.

- [56] Christopher D. Carothers, Kalyan S. Perumalla, and Richard M. Fujimoto. The effect of state-saving in optimistic simulation on a cache-coherent nonuniform memory access architecture. In WSC '99: Proceedings of the 31st conference on Winter simulation, pages 1624–1633, New York, NY, USA, 1999. ACM.

- [57] Ken Mai, Tim Paaske, Nuwan Jayasena, Ron Ho, William J. Dally, and Mark Horowitz. Smart memories: a modular reconfigurable architecture. In *ISCA* '00: Proceedings of the 27th annual international symposium on Computer architecture, pages 161–171, New York, NY, USA, 2000. ACM.

- [58] Richard A. Uhlig and Trevor N. Mudge. Trace-driven memory simulation: a survey. ACM Computing Surveys (CSUR), 29(2):128–170, 1997.

- [59] Michael Laurenzano, Beth Simon, Allan Snavely, and Meghan Gunn. Low cost trace-driven memory simulation using simpoint. ACM SIGARCH Computer Architecture News, 33(5):81–86, 2005.

- [60] V. De La Luz, M. Kandemir, and I. Kolcu. Automatic data migration for reducing energy consumption in multi-bank memory systems. In *DAC '02: Proceedings of the 39th conference on Design automation*, pages 213–218, New York, NY, USA, 2002. ACM.

- [61] Hanene Ben Fradj, Sébastien Icart, Cécile Belleudy, and Michel Auguin. Energy optimization of a multi-bank main memory. In *Proceedings of the 6th International Workshop, Embedded Computer Systems: Architectures, Mod eling, and Simulation (SAMOS)*, pages 196–205, 2006.

- [62] Jorge Navas, Mario Mendez-Lojo, and Manuel Hermenegildo. Safe upperbounds inference of energy consumption for java bytecode applications. In *Proceedings of the sixth NASA Langley Formal Methods Workshop*, pages 29–32. Langley Research Center, 2008.

- [63] Benoit Garbinato, Rachid Guerraoui, Jarle Hulaas, Alexei Kounine, Maxime Monod, and Jesper Honig Spring. The weight-watcher service and its lightweight implementation. In *IC-SAMOS'07: Proceedings of the International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation*, pages 118–127, 2007.

- [64] Benoit Garbinato, Rachid Guerraoui, Jarle Hulaas, Maxime Monod, and Jesper H. Spring. Pervasive computing with frugal objects. In AINAW '07: Proceedings of the 21st International Conference on Advanced Information Networking and Applications Workshops, pages 13–18, Washington, DC, USA, 2007. IEEE Computer Society.

# Part II Original Publications

# Paper I

# An Energy Consumption Model for an Embedded Java Virtual Machine

Sébastien Lafond and Johan Lilius

Originally published in: proceedings of the 19th International Conference on Architecture of Computing Systems - ARCS 2006, Lecture Notes in Computer Science, Vol. 3894, pages 311-325. Springer-Verlag, 2006.

©2006 Springer-Verlag Berlin Heidelberg. Reprinted with permission.

# An Energy Consumption Model for an Embedded Java Virtual Machine

Sébastien Lafond<sup>1</sup> and Johan Lilius<sup>2</sup>

<sup>1</sup> Turku Centre for Computer Science, Embedded Systems Laboratory, Lemminkäisenkatu 14A, FIN-20520 Turku, Finland sebastien.lafond@abo.fi

<sup>2</sup> Åbo Akademi University, Department of Computer Science, Lemminkäinengatan 14A, FIN-20520 Åbo, Finland johan.lilius@abo.fi

**Abstract.** In this paper we establish a general framework for estimating the energy consumption of an embedded Java virtual machine (JVM). We have designed a number of experiments to find the constant overhead of the Virtual Machine and establish an energy consumption cost for individual Java Opcodes. The results show that there is a basic constant overhead for every Java program, and that a subset of Java opcodes have an almost constant energy cost. We also show that memory access is a crucial energy consumption component.

# 1 Introduction

In recent years we have seen an explosion of markets for portable electronic devices such as PDAs, personal communicators and mobile phones. These batteryoperated devices provide more and more functionalities and as a consequence become more and more complex. They have in common strong constraints on energy consumption, and thus maximizing battery life for such devices is crucial.

Several techniques have been developed to optimize the energy consumption of embedded systems. Those techniques can be hardware based solutions, as well as software or co-design solutions [1]. Techniques for low power optimization of software have been mostly applied on processor instructions level [2, 3] by mainly using processor specific instructions [4, 5]. Techniques on memory management have also been widely applied for optimizing energy consumption [6, 7].

At the same time, the size and complexity of applications and development constraints like getting the product to market on time, make necessary the use of high-level languages. Due to the wide diversity of hardware and OS used in the world of handheld devices, portability across systems is not easy and needs efforts. Java language eases portability by allowing application developments with an abstraction of the target platform, making the concept "write once, run it anywhere" possible.

In this paper we establish a general framework for estimating the energy consumption of an embedded Java virtual machine. We present a number of experiments to estimate the constant overhead of the JVM energy consumption and establishe an energy consumption cost for individual Java Opcodes.

W. Grass et al. (Eds.): ARCS 2006, LNCS 3894, pp. 311-325, 2006.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2006

The major contributions of this paper are a better understanding of the energy consumption distribution of an embedded Java virtual machine (JVM) and the definition of the energy cost for the Java bytecodes.

The remainder of this paper is organized as follows. Section 2 proposes a methodology scheme used to characterize the energy consumption of an embedded Java Virtual Machine. Section 3 presents several experiments in order to define some constant overheads of the JVM and comments the repartition of the JVM energy consumption. Section 4 presents a measurement methodology used to define the energy cost of Java bytecode by cost comparison between two appropriate class files. Finally, section 5 concludes the paper and suggests future possible work. This paper is presenting the main results of [8] where more example graphs and results can be found.

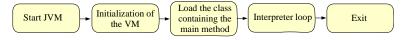

# 2 An Energy Consumption Model of Java Applications

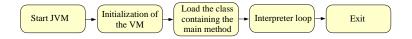

The Java Virtual machine is an abstract machine, making the interface between platform independent applications and the hardware, through a possible operating system. Thus the use of Java language can be seen as adding one more layer, the Java virtual machine, between the hardware and software layers. We want to study how well applying estimation techniques on the virtual machine opcodes level can be done, similarly to what has been done on processor instructions level. Figure 1 shows a simple view of the JVM life cycle. An efficient energy model should characterize each stage of the life cycle model, and thus shows in which stage(s) effort needs to be concentrated to achieve energy optimization. It seems obvious that such model needs to consider the system's hardware and software configuration and therefore is not directly portable. But the methodology used to build it can easily be applied on different configurations by changing the platform configuration parameters.

As shown in [9] the memory consumption must also be included in the model, as the memory might represent the biggest source of energy consumption on a typical embedded system. This is even more important to take into account as the JVM is a stack machine and will therefore have a relatively high memory activity.

Fig. 1. Simple view of the JVM life cycle

#### 2.1 Measurements Methodology

We chose to use the Sun Microsystems K Virtual Machine (KVM), CLDC v1.0.3, as it has been developed for a resource-constrained platform and has its source code freely available. KVM is a small virtual machine containing about 50-80 Kb of object code in its standard configuration and has a total memory footprint

in the range of 128-256 Kb. KVM can run on a 16-bit or 32-bit RISC/CISC processor clocked from 25MHz.

To build an energy model of the KVM we adapted the energy profiler *enpro-filer* [10] developed by the Embedded Systems Groups at Dortmund University. The adaptation was done in order to integrate the Java environment in the results provided by the energy profiler. With the adaptation, when summing up the energy cost for each instruction execution or memory access the *enprofiler* checks in which KVM stage the event occurred and increments the corresponding costs variable. Enprofiler is a processor instructions level energy profiler for ARM7TDMI processor cores operating in Thumb mode [11] and integrating the consumption of memory accesses. It has been built from physical measurements done on an Atmel AT91EB01 evaluation board consisting of a AT91M40400 processor clocked at 33MHz and an external 512K bytes SRAM. A detailed description of the energy model used by *enprofiler* is given in [12]. According to [12] *enprofiler* shows a precision of 1.7% for the cost measurement of 12 instructions in an endless loop.

Figure 2 shows the measurements methodology scheme used to characterize each stage of the KVM life cycle. The Java class generator generates, from template classes, Java applications with the possibility to modify parameters inside the class source code. With the Java Code Compact (JCC) we compile and link together the JVM source code and the generated Java application. The executable code is run on the ARM7TDMI emulator ARMulator, which traces instructions, memory accesses and events that occur during the application execution. From this trace, we extract all information concerning the memory access addresses, size and type (read, write, sequential, non-sequential), the instructions addresses and their corresponding processor opcodes. The energy profiler *enprofiler* reads the emulator trace and accesses databases providing processor instruction costs and the cost of a memory access depending of its address, size

Fig. 2. Measurements methodology scheme

and type. The energy profiler estimates the energy consumed by the application and provides information on how the energy is distributed between the processor and memories for each KVM stage.

# 2.2 Energy Profiler

The energy profiler provides the number of instructions, memory accesses and garbage collections that occur during each KVM stage. It needs as input information on the JVM stage addresses inside the emulator trace. These addresses are provided by the linker from which eight useful address symbols are collected:

- main: this symbol represents the *main()* function of KVM, and is used by the energy profiler to detect the start of the KVM execution.

- StartJVM: represents the StartJVM(argc, argv) function (in StartJVM.c source file). This function only checks if the user gave a class name as argument, and then calls the KVM\_Start() function.

- KVM\_Start: represents the *KVM\_Start()* function (in StartJVM.c source file). This function initializes the VM, the global variables, the profiling variables, the memory system, the hashtable, the class loading interface, the Java system classes, the class file verifier and the event handling system. It also initializes the multithreading system after loading the main application class.

- garbageCollect: represents the garbageCollect() function (in garbage.c source file) that performs a mark-and-sweep garbage collection.

- ExitGarbage : the ExitGarbage symbol was added into the KVM source code in order to detect the end of the garbage collector.

- Interpret : represents the *Interpret()* function (in execute.c source file) that runs the interpreter loop.

- KVM\_Cleanup : KVM\_Cleanup represents the KVM\_Cleanup() function (in StartJVM.c source file). It runs several finalization functions when the VM is shut down.

- ExitVM : This symbol is used to detect the end of the KVM execution.

# **3** Experiments

We have run the measurement process over several representative benchmarks to characterize each stage of the KVM life cycle and determine if some stages are dominant. The benchmarks used are: a) the dhrystone benchmark, b) parts of The Java Grande Forum Benchmark Suite and the DHPC Java Grande Benchmarks. In addition to these established benchmarks we also used as reference an empty application in order to reflect the KVM basic costs. Dedicated intensive allocation applications was also used in order to study the behavior of the KVM stage costs. All benchmarks can be retrieve from [13]. For all measurements, if not explicitly expressed the KVM was compiled with an heap size of 256 Kb.

### 3.1 Benchmarks

*Empty application:* We run the empty application through the measurement process in order to find out if overhead constants in the KVM energy consumption can be determined. We can predict that one or several stage(s), like StartJVM, will have a constant energy consumption, as they have an application independent behavior. Its source code is the following:

```

public class HelloWord {

public static void main(String arg[])

{

//nothing to do

}

}

```

Intensive allocation applications: Two intensive allocation applications were used in order to study a possible application related evolutions in the KVM costs. The first application, called alloc1, instantiates inside a loop one object of class MyClass. This class doesn't contain any field and has just one *main* method. Each new class MyClass created by main is stored in the heap, and will contain only a reference to the class definitions area. Each instantiation will create a new stack frame and call the MyClass constructor which by default will only call java/lang/Object constructor method. The stack frame created by the main method contains two operand stacks and three local variables to store the object reference, the length and the loop index. This application is used to observe the evolution of different KVM stage costs with the length of the loop. The source code for alloc1 is the following:

```

public class MyClass {

public static void main(String arg[])

{

int length = X;

for(int i=0; i<=length ; i++) {

new Myclass();

}

}

}</pre>

```

The second intensive allocation application, called alloc2, is similar to the precedent one with the difference that MyClass contain one field define by an integer array of size 500. Alloc2 is used to observe the weight that can take the garbage collector in comparison to the other KVM stages in extreme allocation rate. As each new instance takes approximatively 2Kb, with an heap size of 128Kb the garbage collector needs to be triggered every 64th objects created in the loop to reclaim the heap space occupied by the unreferenced objects. The source code for alloc2 is the following:

```

316 S. Lafond and J. Lilius

public class MyClass {

int[] tab = new int[500];

public static void main(String arg[])

{

int length = X ;

for(int i=0; i<=length ; i++) {

new Myclass();

}

}

}</pre>

```

*Dhrystone:* Dhrystone tests the system's integer performance. It is a well established benchmark for performance measurement of general purpose system. We conducted the measurement process with two test executions of 50 and 250 benchmark runs.

| Low       | Low level operation benchmarks        |  |  |  |  |

|-----------|---------------------------------------|--|--|--|--|

| Name      | Short description                     |  |  |  |  |

| Arith     | Execution of arithmetic operations    |  |  |  |  |

| Assign    | Variable assignment                   |  |  |  |  |

| Create    | Creating objects and arrays           |  |  |  |  |

| Exception | Exception handling                    |  |  |  |  |

| Loop      | Loop overheads                        |  |  |  |  |

| Math      | Execution of maths library operations |  |  |  |  |

| Method    | Method invocation                     |  |  |  |  |

| Generic   | Local and Static variable handling    |  |  |  |  |

Table 1. Benchmarks used from Java Grande Forum Benchmark suite

Java Grande Benchmarks: We used the sequential benchmarks which are the one suitable for single processor execution. Several low level operation benchmarks was used from the Java Grande Forum Benchmark Suite and the DHPC Java Grande Benchmarks. Table 1 summarize all benchmarks used for our study.

# 3.2 Results

This section presents the results obtained by the introduced applications and benchmarks through the measurement process.

*Empty application:* The empty application has been used in order to find out if overhead constants in the KVM energy consumption can be determined.

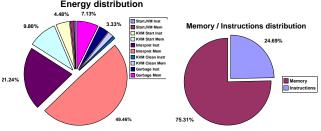

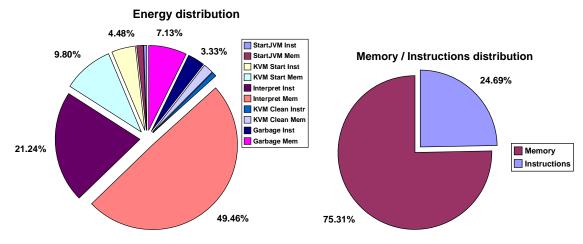

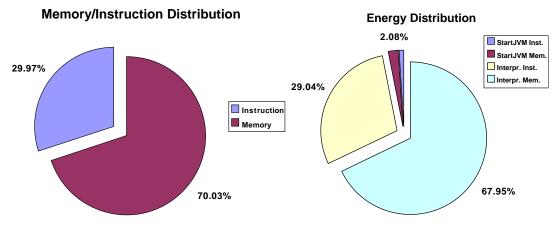

Table 2 shows the obtained results and figure 3 presents the energy consumption distribution among all KVM stages and also the distribution between the energy consumed by memory accesses and processor instruction execution.

We can make some remarks from figure 3. Even if this application does absolutely nothing, it has to be noticed that the interpreter stage represents about

| StartJVM Inst. | StartJVM Mem. | KVMStart Inst.        | KVMStart Mem.                                                                                                   | *               | Interpr. Mem. |

|----------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|---------------|

| 9,42           | 20,08,        | 748,81                | 1639, 18                                                                                                        | 3552,28         | 8273,34       |

|                |               | KVM Clean Inst.       | KVM Clean Mem.                                                                                                  |                 |               |

|                |               | 144,92                | 326,38                                                                                                          |                 |               |

|                |               |                       |                                                                                                                 | -               |               |

|                |               |                       |                                                                                                                 |                 |               |

|                | <b>F</b>      | and the full state of |                                                                                                                 |                 |               |

|                |               | y distribution        |                                                                                                                 |                 |               |

|                | 4.48% 7       | .13%                  | I Contraction of the second |                 |               |

|                | 9.80%         | 3.33% StartJVM Mem    | Memory / Instruction                                                                                            | ns distribution |               |

|                |               | KVM Start Inst        |                                                                                                                 |                 |               |

Table 2. Empty application - Energy consumption of KVM's stages in  $\mu$ J

Fig. 3. Empty Application - Energy consumption distributions

70 % of the consumed energy from all stages, and memory accesses represent 75% of the total consumed energy. As the application was 'empty' the values in table 2 represent the KVM basic costs or the minimal overhead energy cost that any application will have to dissipate.

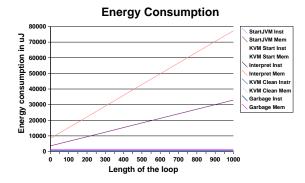

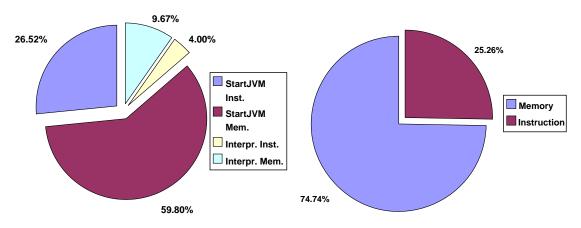

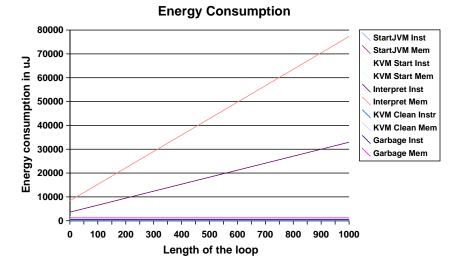

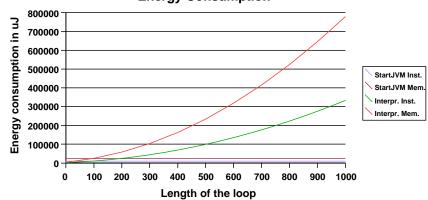

Intensive allocation applications: From the alloc1 results in figure 4 we note that only the energy consumed by the interpreter is dependent on the loop length value. All other stages of the KVM consume a constant energy including the garbage collector, as the maximum number of created object was not enough to fill up the Java heap and trigger off a garbage collection. It is also important to notice that the energy consumed by the interpreter stage is linear and proportional to the loop length. This can be explain by the fact that the interpreter is looping over a number of constant Java opcodes. These opcodes are:

```

4 goto 18

7 new\#2 -> create a new 'MyClass' object in the heap

10 dup -> duplicate new object reference in the operand stack

11 invokespecial \#3 -> call the constructor

14 pop -> remove the top of the operand stack

17 iinc 2 1 -> increment the second local variable by 1

18 iload\_2 -> load 2nd local variable in operand stack (i)

19 iload\_1 -> load 1st local variable in operand stack (length)

20 if\_icmple 65543

```

As the energy profiler evaluates the cost of a memory access according to the memory technology, i.e. have for each memory type (RAM, ROM, Flash, etc.) an average cost for each access type regardless of its address, and as the *new* opcode allocates the same amount of memory for all created (and already resolved) objects, it will have an identical cost for each execution.

Fig. 4. Alloc1 - KVM's stages energy consumption depending of the loop length

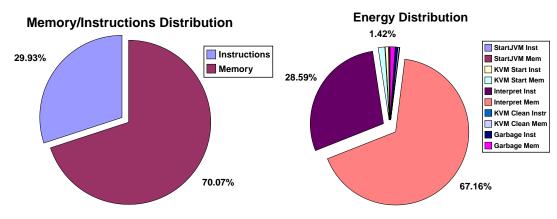

Fig. 5. Alloc1 - Energy distribution for loop length equal to 1000

The energy distribution for a loop length of 1000 presented in figure 5, is similar to the first experiment with an interpreter stage even more dominant, representing over 95% of the total energy consumed.